- 您现在的位置:买卖IC网 > Sheet目录369 > W9751G6IB-25 (Winbond Electronics)IC DDR2-800 SDRAM 512MB 84-WBGA

�� �

�

�

�W9751G6IB�

�7.2.3.1�

�Extended� Mode� Register� for� OCD� Impedance� Adjustment�

�OCD� impedance� adjustment� can� be� done� using� the� following� EMRS� mode.� In� drive� mode� all� outputs�

�are� driven� out� by� DDR2� SDRAM.� In� Drive� (1)� mode,� all� DQ,� DQS� signals� are� driven� HIGH� and� all�

�DQS� signals� are� driven� LOW.� In� Drive� (0)� mode,� all� DQ,� DQS� signals� are� driven� LOW� and� all� DQS�

�signals� are� driven� HIGH.� In� adjust� mode,� BL� =� 4� of� operation� code� data� must� be� used.� In� case� of� OCD�

�calibration� default,� output� driver� characteristics� have� a� nominal� impedance� value� of� 18� Ohms� during�

�nominal� temperature� and� voltage� conditions.� OCD� applies� only� to� normal� full� strength� output� drive�

�setting� defined� by� EMR� (1)� and� if� reduced� strength� is� set,� OCD� default� driver� characteristics� are� not�

�applicable.� When� OCD� calibration� adjust� mode� is� used,� OCD� default� output� driver� characteristics� are�

�not� applicable.� After� OCD� calibration� is� completed� or� driver� strength� is� set� to� default,� subsequent�

�EMRS� commands� not� intended� to� adjust� OCD� characteristics� must� specify� A[9:7]� as� ’000’� in� order� to�

�maintain� the� default� or� calibrated� value.�

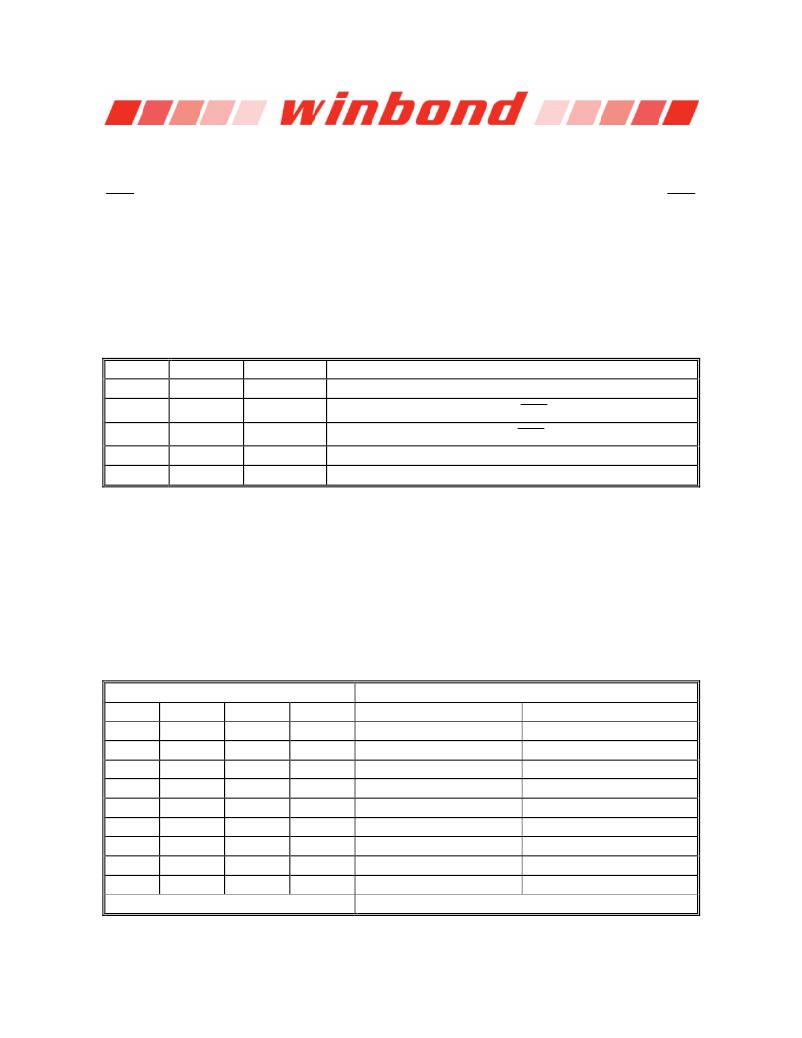

�Table� 1� —� OCD� Drive� Mode� Program�

�A9�

�0�

�0�

�0�

�1�

�1�

�A8�

�0�

�0�

�1�

�0�

�1�

�A7�

�0�

�1�

�0�

�0�

�1�

�Operation�

�OCD� calibration� mode� exit�

�Drive� (1)� DQ,� DQS� HIGH� and� DQS� LOW�

�Drive� (0)� DQ,� DQS� LOW� and� DQS� HIGH�

�Adjust� mode�

�OCD� calibration� default�

�7.2.3.2�

�OCD� Impedance� Adjust�

�To� adjust� output� driver� impedance,� controllers� must� issue� the� ADJUST� EMRS� command� along� with� a�

�4� bit� burst� code� to� DDR2� SDRAM� as� in� table� 2.� For� this� operation,� Burst� Length� has� to� be� set� to� BL� =�

�4� via� MRS� command� before� activating� OCD� and� controllers� must� drive� the� burst� code� to� all� DQs� at� the�

�same� time.� D� T0� in� table� 2� means� all� DQ� bits� at� bit� time� 0,� D� T1� at� bit� time� 1,� and� so� forth.� The� driver�

�output� impedance� is� adjusted� for� all� DDR2� SDRAM� DQs� simultaneously� and� after� OCD� calibration,� all�

�DQs� and� DQS’s� of� a� given� DDR2� SDRAM� will� be� adjusted� to� the� same� driver� strength� setting.� The�

�maximum� step� count� for� adjustment� is� 16� and� when� the� limit� is� reached,� further� increment� or�

�decrement� code� has� no� effect.� The� default� setting� may� be� any� step� within� the� 16� step� range.� When�

�Adjust� mode� command� is� issued,� AL� from� previously� set� value� must� be� applied.�

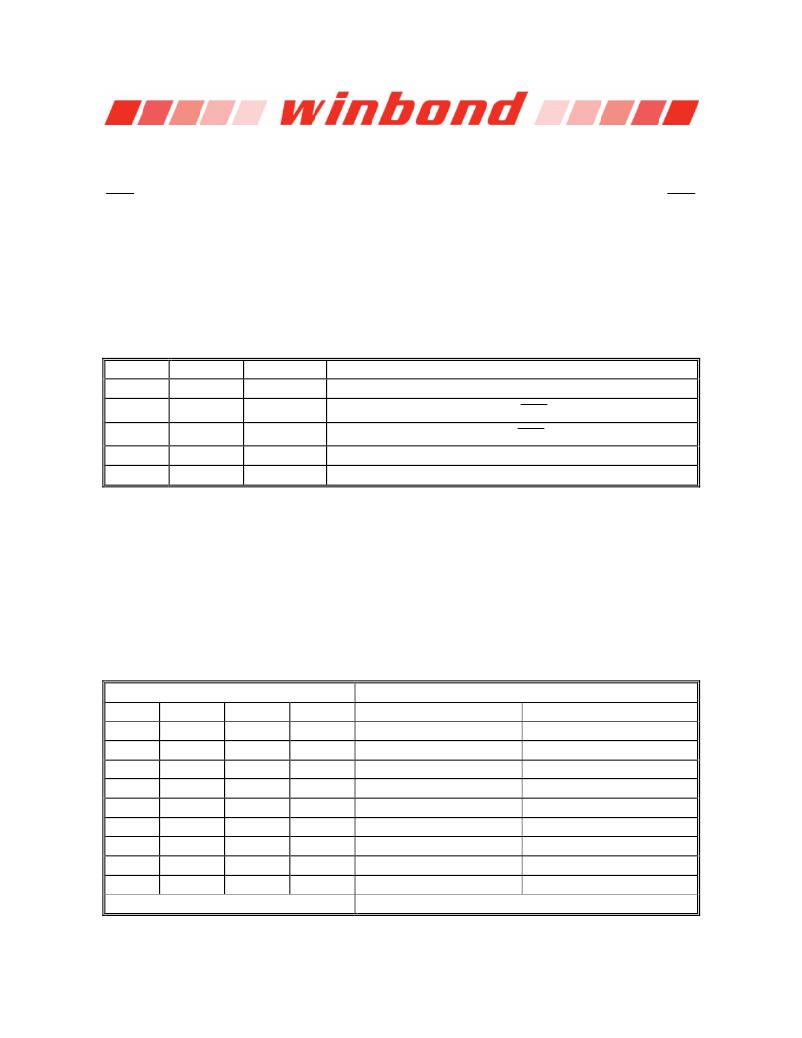

�Table� 2� —� OCD� Adjust� Mode� Program�

�4� bit� b� urst code� inputs� to� all� DQs�

�Operation�

�D� T0�

�D� T1�

�D� T2�

�D� T3�

�Pull-up� driver� strength�

�Pull-down� driver� strength�

�0� 0� 0� 0�

�0� 0� 0� 1�

�0� 0� 1� 0�

�0� 1� 0� 0�

�1� 0� 0� 0�

�0� 1� 0� 1�

�0� 1� 1� 0�

�1� 0� 0� 1�

�1� 0� 1� 0�

�Other� Combinations�

�NOP� (No� operation)� NOP� (No� operation)�

�Increase� by� 1� step� NOP�

�Decrease� by� 1� step� NOP�

�NOP� Increase� by� 1� step�

�NOP� Decrease� by� 1� step�

�Increase� by� 1� step� Increase� by� 1� step�

�Decrease� by� 1� step� Increase� by� 1� step�

�Increase� by� 1� step� Decrease� by� 1� step�

�Decrease� by� 1� step� Decrease� by� 1� step�

�Reserved�

�Publication� Release� Date:� Oct.� 23,� 2009�

�-� 16� -�

�Revision� A06�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

W9751G6KB-25

IC DDR2 SDRAM 512MBIT 84WBGA

W9812G6JH-6I

IC SDRAM 128MBIT 54TSOPII

W9816G6IH-6I

IC SDRAM 16MBIT 50TSOPII

W9825G6JH-6I

IC SDRAM 256MBIT 54TSOPII

W9864G6JH-6I

IC SDRAM 64MBIT 54TSOPII

WM-5614

CABINET WALL MOUNT 37.25X17.9"

WRR-2244

RACK WALL MOUNT RELAY 42" X 19"

WRR-2264

RACK WALL MOUNT 75.25" X 19"

相关代理商/技术参数

W9751G6JB

制造商:WINBOND 制造商全称:Winbond 功能描述:8M ? 4 BANKS ? 16 BIT DDR2 SDRAM

W9751G6JB-25

制造商:Winbond Electronics Corp 功能描述:512GB DDRII

W9751G6JB-3

制造商:Winbond Electronics Corp 功能描述:512MB DDRII

W9751G6KB

制造商:WINBOND 制造商全称:Winbond 功能描述:8M ? 4 BANKS ? 16 BIT DDR2 SDRAM

W9751G6KB-18

制造商:Winbond Electronics Corp 功能描述:IC MEMORY

W9751G6KB-25

功能描述:IC DDR2 SDRAM 512MBIT 84WBGA RoHS:是 类别:集成电路 (IC) >> 存储器 系列:- 标准包装:1 系列:- 格式 - 存储器:闪存 存储器类型:闪存 - NAND 存储容量:4G(256M x 16) 速度:- 接口:并联 电源电压:2.7 V ~ 3.6 V 工作温度:0°C ~ 70°C 封装/外壳:48-TFSOP(0.724",18.40mm 宽) 供应商设备封装:48-TSOP I 包装:Digi-Reel® 其它名称:557-1461-6

W9751G6KB25A

制造商:WINBOND 制造商全称:Winbond 功能描述:Double Data Rate architecture: two data transfers per clock cycle

W9751G6KB25I

制造商:Winbond Electronics Corp 功能描述:DRAM Chip DDR2 SDRAM 512M-Bit 32Mx16 1.8V 84-Pin WBGA 制造商:Winbond Electronics Corp 功能描述:IC DDR2 SDRAM 512MBIT 2.5NS BGA